# R&S<sup>®</sup>RTO-K26 D-PHY Compliance Test Test Procedures

Test Procedures

Test & Measurement

This manual describes the D-PHY compliance test procedures with the following option:

• R&S®RTO-K26 (1317.5668.02) - D-PHY

The tests require the R&S ScopeSuite software.

The software contained in this product makes use of several valuable open source software packages. For information, see the "Open Source Acknowledgement" document, which is available for download from the R&S RTO product page at http://www.rohde-schwarz.com/product/rto.html > "Software".

Rohde & Schwarz would like to thank the open source community for their valuable contribution to embedded computing.

© 2016 Rohde & Schwarz GmbH & Co. KG Mühldorfstr. 15, 81671 München, Germany Phone: +49 89 41 29 - 0 Fax: +49 89 41 29 12 164 Email: info@rohde-schwarz.com Internet: www.rohde-schwarz.com Subject to change – Data without tolerance limits is not binding. R&S<sup>®</sup> is a registered trademark of Rohde & Schwarz GmbH & Co. KG.

Trade names are trademarks of the owners.

The following abbreviations are used throughout this manual: R&S<sup>®</sup>RTO is abbreviated as R&S RTO, and R&S<sup>®</sup>ScopeSuite is abbreviated as R&S ScopeSuite.

## Contents

| 1     | R&S ScopeSuite Overview                           | . 5 |

|-------|---------------------------------------------------|-----|

| 2     | Preparing the Measurements                        | .7  |

| 2.1   | Test Equipment                                    | . 7 |

| 2.2   | Installing Software and License                   | . 7 |

| 2.3   | Setting Up the Network                            | 8   |

| 2.4   | Starting the R&S ScopeSuite                       | . 9 |

| 2.5   | Connecting the R&S RTO                            | .9  |

| 2.6   | Report Configuration                              | 10  |

| 3     | Performing Tests                                  | 12  |

| 3.1   | Starting a Test Session                           | 12  |

| 3.2   | Configuring the Test                              | 13  |

| 3.2.1 | General Test Settings                             | 13  |

| 3.3   | Getting Test Results                              | 15  |

| 4     | D-PHY Compliance Tests1                           | 17  |

| 4.1   | Starting D-PHY Compliance Tests                   | 19  |

| 4.2   | Test Configuration for D-PHY                      | 19  |

| 4.3   | Data Lane LP-TX Signaling Requirements (Group 1)  | 23  |

| 4.3.1 | Test Setup                                        | 23  |

| 4.3.2 | Performing Group 1 Test Cases                     | 25  |

| 4.3.3 | Measurements                                      | 26  |

| 4.4   | Clock Lane LP-TX Signaling Requirements (Group 2) | 33  |

| 4.4.1 | Test Setup                                        | 34  |

| 4.4.2 | Performing Group 2 Test Cases                     | 35  |

| 4.4.3 | Measurements                                      | 36  |

| 4.5   | Data Lane HS-TX Signaling Requirements (Group 3)  | 42  |

| 4.5.1 | Test Setup                                        | 42  |

| 4.5.2 | Performing Group 3 Test Cases                     | 46  |

| 4.5.3 | Measurements                                      | 47  |

| 4.6   | Clock Lane HS-TX Signaling Requirements (Group 4) | 66  |

| 4.6.1 | Test Setup                                        | 67  |

| 4.6.2 | Performing Group 4 Test Cases                          | . 70 |

|-------|--------------------------------------------------------|------|

| 4.6.3 | Measurements                                           | . 71 |

| 4.7   | HS-TX Clock-to-Data Lane Timing Requirements (Group 5) | .91  |

| 4.7.1 | Test Setup                                             | .92  |

| 4.7.2 | Performing Group 5 Test Cases                          | . 95 |

| 4.7.3 | Measurements                                           | . 96 |

|       |                                                        |      |

## 1 R&S ScopeSuite Overview

The R&S ScopeSuite software is used with R&S RTO oscilloscopes. It can be installed on a test computer or directly on the R&S RTO if the instrument has the Windows 7 operating system.

| RSScopeSuite       |                         |            |              |          | _ 🗆 🗙  |

|--------------------|-------------------------|------------|--------------|----------|--------|

|                    |                         |            | Tile View    | () About | 🕐 Help |

| Settings           | Compliance Te           | sts        | 📌 BroadR-R   | each     |        |

|                    |                         |            | 📌 Demo       |          |        |

|                    | ***                     |            | 📌 D-PHY      |          |        |

|                    | <b></b>                 |            | 📌 eMMC       |          |        |

| Oscilloscope       | BroadR-Reach            | D-PHY      | 📌 Ethernet   |          |        |

|                    |                         |            | 📌 Ethernet : | LOG      |        |

| Ö.                 |                         |            | 📌 USB 2.0    |          |        |

| · · · · ·          | _                       | 1 <b>G</b> | 📌 Unpin All  |          |        |

| Instruments        | eMMC                    | Ethernet   |              |          |        |

| Report             | Ethernet 10G            | USB        |              |          |        |

| Report             | Ethemet 100             | 030        |              |          |        |

|                    | Demo                    |            |              |          |        |

| Welcome to complia | nce tests selection scr | een.       |              |          |        |

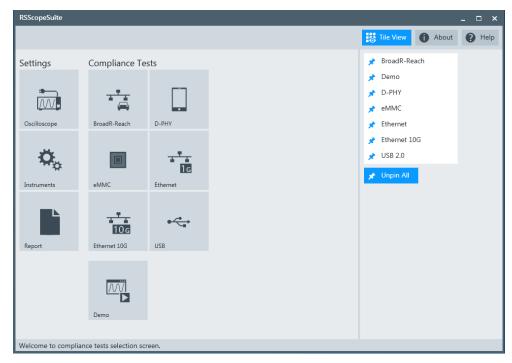

The R&S ScopeSuite main panel has several areas:

- "Settings": connection settings to oscilloscope and other instruments as well as default report settings

- "Compliance Tests": selection of the compliance test

- "Demo": accesses demo test cases that can be used for trying out the software without having a connection to an oscilloscope

- "Help": opens the help file, conatining information about the R&S ScopeSuite configuration

- "About": gives information about the R&S ScopeSuite software

- "Tile View": allows a personalization of the compliance test selection You can configure which tests are visible in the compliance test section and which are hidden, so that only the ones you use are displayed.

- ► To hide a test from the "Compliance Tests" view do one of the following:

Right-click on the compliance test you want to hide.

The icon of the test changes, see Figure 1-1. Now with a left click you can hide the test

Figure 1-1: Unpin icon

b) Click on "Title View" to show a list of the available test cases. By clicking on a test case in the show list you can pin/unpin it from the main panel.

## 2 Preparing the Measurements

## 2.1 Test Equipment

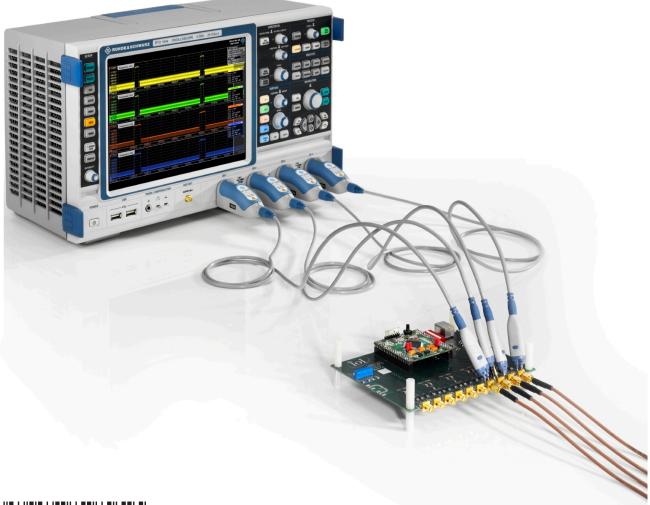

For D-PHY compliance tests, the following test equipment is needed:

- R&S RTO oscilloscope with 4 channels and at least 4 GHz bandwidth

- For measuring the clock signal (+ and -): either 1 differential probe or 2 singleended probes with at least 4 GHz bandwidth. However, note that D-PHY Group 2 and Group 4 tests require 2 probes for the clock signal.

- For measuring the data signal (+ and -): 2 probes with at least 4 GHz bandwidth

- R&S RTO-K26 D-PHY compliance test option (required option, installed on the R&S RTO)

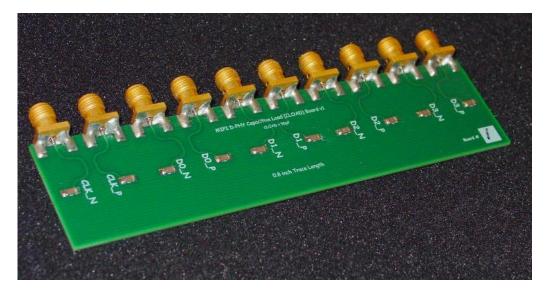

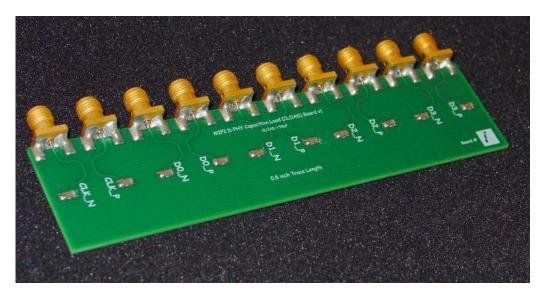

- Recommended test fixture for LP-TX tests: MIPI D-PHY Capacitive Load (C<sub>LOAD</sub>) Fixture from The University of New Hampshire InterOperability Laboratory (UNH-IOL)

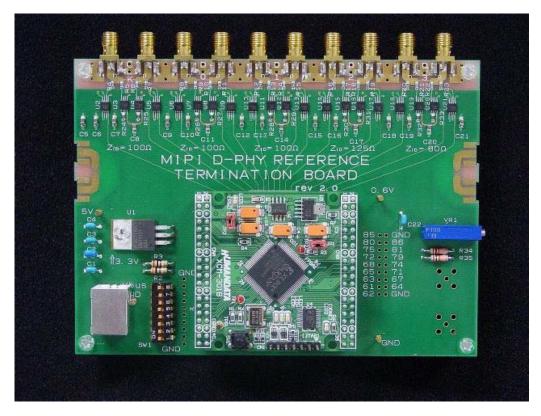

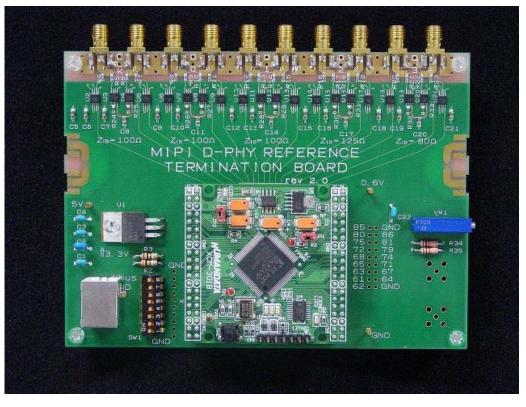

- Recommended termination board for HS-TX tests: MIPI D-PHY Reference Termination Board (RTB) from The University of New Hampshire InterOperability Laboratory (UNH-IOL)

- The free-of-charge R&S ScopeSuite software, which can be installed on a computer or directly on the R&S RTO.

### 2.2 Installing Software and License

The preparation steps have to be performed only once for each computer and instrument that are used for testing.

### NOTICE

#### Uninstall older versions of the R&S ScopeSuite

If an older version of the R&S ScopeSuite is installed, make sure to uninstall the old version before you install the new one. You can find the version number of the current installation in "Help" menu > "About". To uninstall the R&S ScopeSuite, use the Windows Control Panel > "Programs".

#### To install the R&S ScopeSuite

- Download the R&S ScopeSuite software from the "Software" section on the Rohde & Schwarz R&S RTO website: www.rohde-schwarz.com/product/rto.html.

- 2. Install the R&S ScopeSuite software:

- Either on the computer that is used for testing,

- or on the R&S RTO if the instrument has a Windows 7 operating system.

#### To install the license key on the R&S RTO

When you got the license key of the compliance test option, enable it on the R&S RTO using SETUP > "SW Options".

For a detailed description, refer to the R&S RTO User Manual, chapter "Installing Options", or to the online help on the instrument.

## 2.3 Setting Up the Network

If the R&S ScopeSuite software runs on a test computer, the computer and the testing R&S RTO require a LAN connection.

For some test cases, you need an additional instrument: arbitrary waveform generator (AWG), vector network analyzer (VNA), or spectrum analyzer. These instruments can be used in automatic or manual mode. For automatic testing, a LAN connection to the additional instrument is required.

There are two ways of connection:

- LAN (local area network): It is recommended that you connect to a LAN with DHCP server. This server uses the Dynamic Host Configuration Protocol (DHCP) to assign all address information automatically.

If no DHCP server is available, or if the Tabor WX2182B is used for automatic testing, assign fixed IP adresses to all devices.

- Direct connection of the instruments and the computer or connection to a switch using LAN cables: Assign fixed IP addresses to the computer and the instruments and reboot all devices.

#### To set up and test the LAN connection

- 1. Connect the computer and the instruments to the same LAN.

- 2. Start all devices.

- 3. If no DHCP server is available, assign fixed IP addresses to all devices.

- 4. Ping the instruments to make sure that the connection has been established.

- 5. If VISA is installed, check if VISA can access the instruments.

- a) Start VISA on the test computer.

- b) Validate the VISA address string of each device.

See also:

Chapter 2.5, "Connecting the R&S RTO", on page 9

## 2.4 Starting the R&S ScopeSuite

To start the R&S ScopeSuite on the test computer or on the oscilloscope:

Double-click the R&S ScopeSuite program icon.

To start the R&S ScopeSuite on the instrument, in the R&S RTO firmware:

▶ On the "Analysis" menu, tap "Start Compliance Test".

## 2.5 Connecting the R&S RTO

If the R&S ScopeSuite is installed directly on the instrument, the software detects the R&S RTO firmware automatically, and the "Oscilloscope" button is not available in the R&S ScopeSuite.

If the R&S ScopeSuite software runs on a test computer, the computer and the testing R&S RTO require a LAN connection, see Chapter 2.3, "Setting Up the Network", on page 8. The R&S ScopeSuite software needs the IP address of the R&S RTO to establish connection.

- 1. Start the R&S RTO.

- 2. Start the R&S ScopeSuite software.

- 3. Click "Settings" > "Osilloscope".

4. Enter the IP address of the R&S RTO.

To obtain the IP address: Press the SETUP key on the instrument and tap the "System" tab.

5. Click "Get Instrument Information".

The computer connects with the instrument and gets the instrument data.

| RSScopeSuite                  |                            |       | _ 🗆 ×  |

|-------------------------------|----------------------------|-------|--------|

| G Back Oscilloscope           | Settings                   | About | P Help |

| Oscilloscope<br>IP address:   | 10.113.10.30               |       |        |

|                               | Get Instrument Information |       |        |

| Device:                       | RTO                        |       |        |

| Serial Number:                | 400132                     |       |        |

| Firmware Version:             | 2.60.2.7                   |       |        |

| Restore Settings On Exit:     | ● Never ○ Ask ○ Always     |       |        |

|                               |                            |       |        |

|                               |                            |       |        |

|                               |                            |       |        |

|                               |                            |       |        |

|                               |                            |       |        |

|                               |                            |       |        |

| Connect software to your RTO. |                            |       |        |

If the connection fails, an error message is shown.

## 2.6 Report Configuration

In the "Report Configuration" menu, you can select the format of the report and the details to be included in the report. You can also select an icon that will be displayed in the upper left corner of the report.

Additionally, you can enter common information on the test that will be written in the "General Information" section of the test report.

Report Configuration

| RSScopeSuite                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |      |   |    |        |   |       | _ | ⊐ ×  |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|---|----|--------|---|-------|---|------|

| G Back Report Settings                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |      |   |    |        | 0 | About | 0 | Help |

| Content                               | Format                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 | Icon |   |    |        |   |       |   |      |

| Display Summary 🚽                     | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | PDF             |      |   | 63 | Change |   |       |   |      |

| Display Detail 🚽                      | <ul> <li>Image: A start of the start of</li></ul> | O Word Document |      | V |    |        |   |       |   |      |

| Display Screenshots 🚽                 | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                 |      |   |    |        |   |       |   |      |

| User Input<br>Device Under Test (DUT) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |      |   |    |        |   |       |   |      |

| User                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |      |   |    |        |   |       |   |      |

| Site                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |      |   |    |        |   |       |   |      |

| Temperature                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |      |   |    |        |   |       |   |      |

| Comments                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |      |   |    |        |   |       |   |      |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |      |   |    |        |   |       |   |      |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |      |   |    |        |   |       |   |      |

|                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                 |      |   |    |        |   |       |   |      |

| Configure default settings for new s  | ession                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                 |      |   |    |        |   |       |   |      |

## 3 Performing Tests

## 3.1 Starting a Test Session

| RSScopeSuite           |                       |                 |               | _            |

|------------------------|-----------------------|-----------------|---------------|--------------|

| 🕒 Back Comp            | liance Tests D-PHY    |                 |               | About P Help |

| Session Name           | Last Accessed         | Comment         |               |              |

| Test10-31              | 12/21/2015 4:41:16 PM | DUT Nr. 300     |               |              |

| Test10-30              | 12/21/2015 3:43:54 PM | DUT Nr. 234     |               |              |

|                        |                       |                 |               |              |

|                        |                       |                 |               |              |

|                        |                       |                 |               |              |

|                        |                       |                 |               |              |

|                        |                       |                 |               |              |

|                        |                       |                 |               |              |

|                        |                       |                 |               |              |

|                        |                       |                 |               |              |

|                        |                       |                 |               |              |

|                        |                       |                 |               |              |

|                        |                       |                 |               |              |

|                        |                       |                 |               |              |

|                        |                       |                 |               |              |

| 🕂 Add  🖬 Op            | en 💼 Remove 🖳 R       | ename 📑 Comment | 🖹 Show Report |              |

| dd new or open existir | ng session to run.    |                 |               |              |

After you open a compliance test the "Session Selection" dialog appears. In this dialog you can create new sessions, open or view existing report.

The following functions are available for handling test sessions:

| Function      | Description                                 |

|---------------|---------------------------------------------|

| "Add"         | Adds a new session                          |

| "Open"        | Opens the selected session                  |

| "Remove"      | Removes the selected session                |

| "Rename"      | Changes the "Session Name"                  |

| "Comment"     | Adds a comment                              |

| "Show report" | Generates a report for the selected session |

## 3.2 Configuring the Test

- 1. In the R&S ScopeSuite window, select the compliance test to be performed:

- "D-PHY"

- 2. Open a test session, see Chapter 3.1, "Starting a Test Session", on page 12.

- 3. Adjust the "Properties" settings for the test cases you want to perform.

- 4. Click "Limit Manager" and edit the limit criterias, see Chapter 3.2.1.1, "Limit Manager", on page 14.

- If you want to use special report settings the "Report Config" tab to define the format and contents of the report. Otherwise the settings defined in "RSScopeSuite" > "Settings" > "Report" will be used. See Chapter 2.6, "Report Configuration", on page 10.

- 6. Click "Test Checked"/"Test Single" and proceed as descibed in the relevant test case chapter.

#### 3.2.1 General Test Settings

| RSScopeSuit   | e                                                                     |                             |                                                               |                                     |                  |         | _ 🗆 🗙  |

|---------------|-----------------------------------------------------------------------|-----------------------------|---------------------------------------------------------------|-------------------------------------|------------------|---------|--------|

| 🕒 Back        | Session D-PHY_20160205_110028                                         |                             |                                                               | 🖹 Sh                                | ow Report        | 1 About | 🕜 Help |

| <b>•</b>      | All                                                                   | Properties                  | Limit Manager                                                 | Results                             | Report Cor       | nfig    |        |

|               | <ul> <li>Data Lane LP-TX Signaling Requirements (Group 1)</li> </ul>  | DUT Setti                   | ngs                                                           |                                     |                  |         |        |

|               | <ul> <li>Clock Lane LP-TX Signaling Requirements (Group 2)</li> </ul> |                             |                                                               | <u> </u>                            |                  |         |        |

|               | <ul> <li>Data Lane HS-TX Signaling Requirements (Group 3)</li> </ul>  |                             | Camer                                                         | a 🔿 Displa                          | У                |         |        |

|               | ▼ Clock Lane HS-TX Signaling Requirements (Group 4)                   |                             | Bitrat                                                        | e 0 M                               | lbps             |         |        |

|               | ▼ HS Clock-To-Data Lane Timing Requirements (Group                    |                             | Clock Typ                                                     | e Normal B                          | urst 🔻           |         |        |

| 3             |                                                                       | Test Setu<br>∪s<br>Debuggir | Data Lan<br>Z I<br>C LOA<br>Probe Confi<br>e Previous Setting | b 100 ▼<br>b 50 pF<br>g < 4 ▼<br>is | Ω<br>▼<br>probes |         |        |

| Test Ch       | necked                                                                |                             |                                                               |                                     |                  |         |        |

| Ready to run. |                                                                       |                             |                                                               |                                     |                  |         |        |

Each session dialog is divided into several sections:

"Properties": shows the settings that can be made for the test case selected on the left side of the dialog. You can differentiate between the "All" and the sub test properties

In the "All" > "Properties" tab you can configure the settings for all test cases in the current session. Once you change and save a setting in this tab the changes will be done for all test in the sessions. At the same time there will be a special marking for the functions that have different settings for different sub tests.

- "Limit Manager": sets the measurement limits that are used for compliance testing, see Chapter 3.2.1.1, "Limit Manager", on page 14.

- "Results": shows an overview of the available test results for this session.

- "Instruments": defines instruments settings for connecting to external devices, that are specific for this t est session.

When a session is first created the global settings ("RSScopeSuite" > "Settings" > "Instruments") are copied to the session. This "Instruments" tab can be used to change those copied defaults.

- "Report Config": defines the format and contents of the report for this session. When a session is first created the global settings ("RSScopeSuite" > "Settings" > "Report") are copied to the session. This "Report Config" tab can be used to change those copied defaults.

- "Test Checked"/ "Test Single": starts the selected test group.

#### 3.2.1.1 Limit Manager

The "Limit Manager" shows the measurement limits that are used for compliance testing.

Each limit comprises the comparison criterion, the unit, the limit value A, and a second limit value B if the criterion requires two limits.

You can set the values to defaults, change the values in the table, export the table in xml format, or import xml files with limit settings.

Check and adjust the measurement limits.

Getting Test Results

| Measurement         Criteria         Unit         A         B           T_LPX $x >= A$ s         5E-08            V_OD(1) $A <= x <= B$ V         0.14         0.27           V_OD(0) $A <= x <= B$ V         -0.27         -0.14           d_V_OD(0) $A <= x <= B$ V         0.014            V_OD(0) $X <= A$ V         0.36            V_OHHS(DP) $x <= A$ V         0.36            V_OHHS(DN) $x <= A$ V         0.15         0.25           V_CMTX(1) $A <= x <= B$ V         0.15         0.25           d_V_CMTX(L) $X <= A$ V         0.005            d_V_CMTX(LF) PEAK $x <= A$ V         0.025            d_V_CMTX(HF) RMS $x <= A$ V         0.015 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V_OD(1)       A<=x<=B •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| V_OD(0)       A<=x<=B •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| d_V_OD     x<=A     V     0.014       V_OHHS(DP)     x<=A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V_OHHS(DP)     x<=A ▼     V     0.36       V_OHHS(DN)     x<=A ▼                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| V_OHHS(DN)       x<=A       V       0.36         V_CMTX(1)       A<=x<=B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V_CMTX(1)       A<=x<=B       V       0.15       0.25         V_CMTX(0)       A<=x<=B       V       0.15       0.25         d_V_CMTX(1,0)       x<=A       V       0.005       0.25         d_V_CMTX(LF) PEAK       x<=A       V       0.025                                                                                                                                                                                                                                                                                                                                                                                                                    |

| V_CMTX(0)       A<=x<=B ▼       V       0.15       0.25         d_V_CMTX(1,0)       x<=A ▼                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| d_V_CMTX(1,0) x<=A ▼ V 0.005<br>d_V_CMTX(LF) PEAK x<=A ▼ V 0.025                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| d_V_CMTX(LF) PEAK x<=A ▼ V 0.025                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| d V CMTX(HE) RMS V<=A V 0.015                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| T_REOT x<=A ▼ s 3.5E-08                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| T_HS-EXIT x>=A ▼ s 1E-07                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| T_SKEW A<=x<=B ▼ % -15 15                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| V_OH A<=x<=B ▼ V 1.1 1.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| V_OL A<=x<=B ▼ V -0.05 0.05                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

### 3.3 Getting Test Results

For each test, the test data - report, diagrams and waveform files - is saved in the following folder:

%ProgramData%\Rohde-Schwarz\RSScopeSuite2\Sessions\D-PHY\<Session Name>

If you resume an existing session, new measurements are appended to the report, new diagrams and waveform files are added to the session folder. Existing files are not deleted or replaced. Sessions data remain until you delete them in the "Results" tab of the session.

The report format can be defined in "RSScopeSuite" > "Settings" > "Report" for all compliance tests (see also Chapter 2.6, "Report Configuration", on page 10). If you want to use special report settings for a session, you can define the format and contents of the report in the "Report Config" tab of the session.

All test results are listed in the "Results" tab. Reports can be provided in PDF, MSWord, or HTML format. To view and print PDF reports, you need a PDF viewer, for example, the Acrobat Reader.

The test report file can be created at the end of the test, or later in the "Session Selection" dialog.

#### To show a test report

- 1. In the R&S ScopeSuite window, select the compliance test to be performed.

- 2. Select the session name in the "Session Selection" dialog and click "Show report".

The report opens in a separate application window, depending on the file format. You can check the test results and print the report.

#### To delete the results, diagrams and waveform files of a session

- 1. In the "Session Selection" dialog select the session and open it.

- 2. In the "Results" tab, select the result to be deleted.

- 3. Click "Remove".

## 4 D-PHY Compliance Tests

D-PHY Ethernet compliance tests require option R&S RTO-K26.

The software closely follows the MIPI Alliance's **Conformance Test Suite for D-PHY Physical Layer Version 1.1 Revision 03**, dated June 5<sup>th</sup>, 2013. Should anything remain unclear in this manual, please refer to that CTS document, which is available for members of the MIPI Alliance at https://members.mipi.org/wg/All-Members/home/ approved-specs.

Table 4-1: Overview of D-PHY compliance tests

| Test Groups and Tests                                                                            | see  |

|--------------------------------------------------------------------------------------------------|------|

| Group 1 (7 tests): Data Lane LP-TX Signaling Requirements                                        | page |

| 1.1.1 – Data Lane LP-TX Thevenin Output High Level Voltage ( $V_{OH}$ )                          | 23   |

| 1.1.2 – Data Lane LP-TX Thevenin Output Low Level Voltage (V <sub>OL</sub> )                     |      |

| 1.1.3 – Data Lane LP-TX 15%-85% Rise Time (T <sub>RLP</sub> )                                    |      |

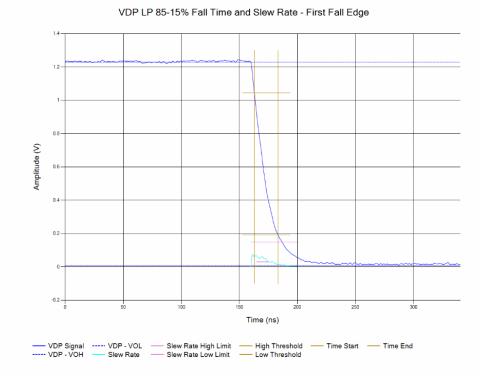

| 1.1.4 – Data Lane LP-TX 85%-15% Fall Time (T <sub>FLP</sub> )                                    |      |

| 1.1.5 – Data Lane LP-TX Slew Rate vs. $C_{LOAD}$ ( $\delta V / \delta t_{SR}$ )                  |      |

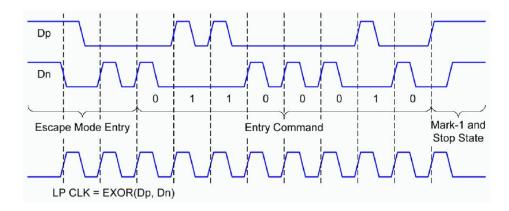

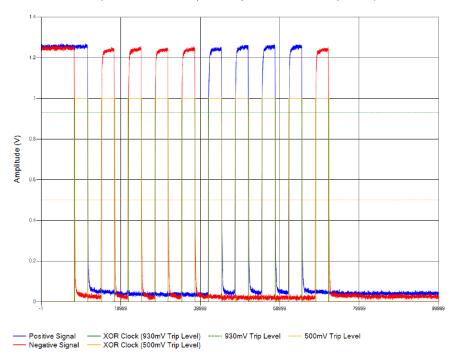

| 1.1.6 – Data Lane LP-TX Pulse Width of Exclusive-OR Clock (T <sub>LP-PULSE-TX</sub> )            |      |

| 1.1.7 – Data Lane LP-TX Period of Exclusive-OR Clock (T <sub>LP-PER-TX</sub> )                   |      |

| Group 2 (5 tests): Clock Lane LP-TX Signaling Requirements                                       | page |

| 1.2.1 – Clock Lane LP-TX Thevenin Output High Level Voltage ( $V_{OH}$ )                         | 33   |

| 1.2.2 – Clock Lane LP-TX Thevenin Output Low Level Voltage ( $V_{OL}$ )                          |      |

| 1.2.3 – Clock Lane LP-TX 15%-85% Rise Time (T <sub>RLP</sub> )                                   |      |

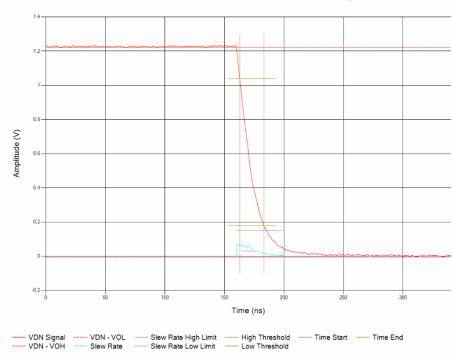

| 1.2.4 – Clock Lane LP-TX 85%-15% Fall Time (T <sub>FLP</sub> )                                   |      |

| 1.2.5 – Clock Lane LP-TX Slew Rate vs. $C_{LOAD}$ ( $\delta V / \delta t_{SR}$ )                 |      |

| Group 3 (16 tests): Data Lane HS-TX Signaling Requirements                                       | page |

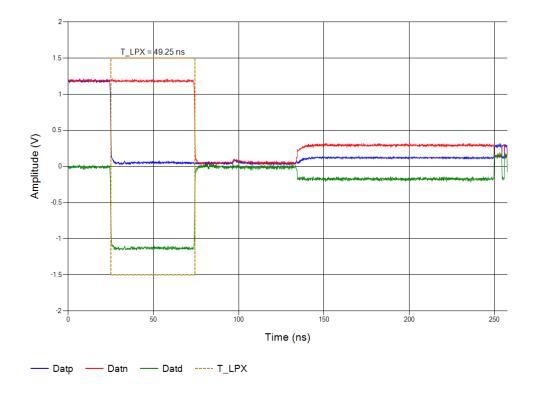

| 1.3.1 – Data Lane HS Entry: Data Lane T <sub>LPX</sub> Value                                     | 42   |

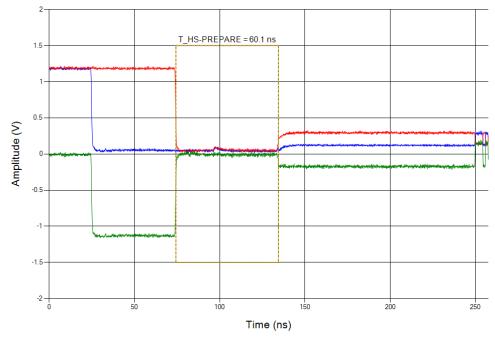

| 1.3.2 – Data Lane HS Entry: Data Lane T <sub>HS-PREPARE</sub> Value                              |      |

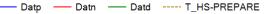

| 1.3.3 – Data Lane HS Entry: Data Lane T <sub>HS-PREPARE</sub> + T <sub>HS-ZERO</sub> Value       |      |

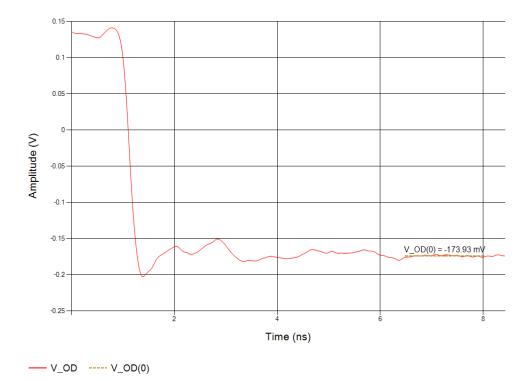

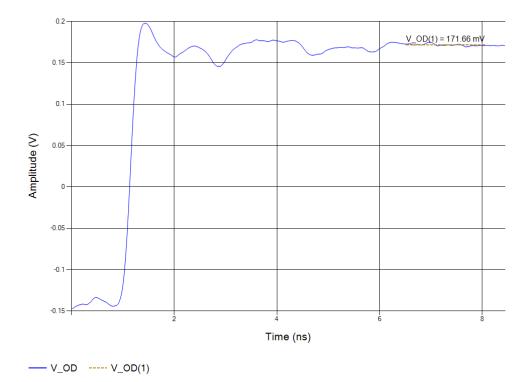

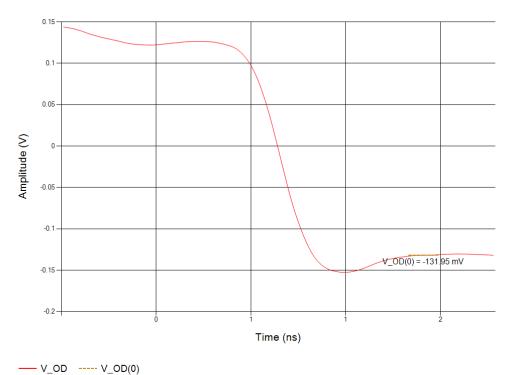

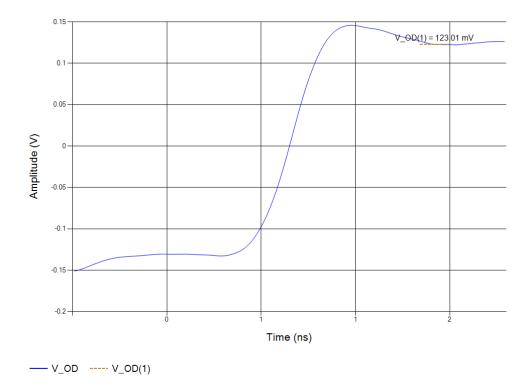

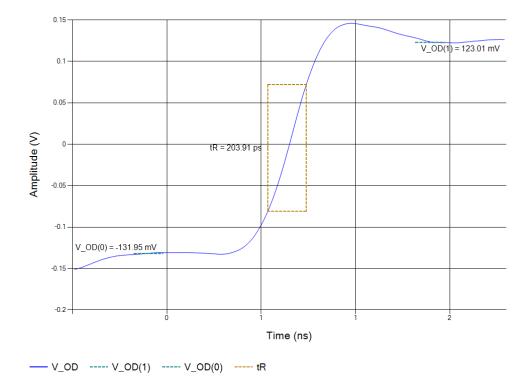

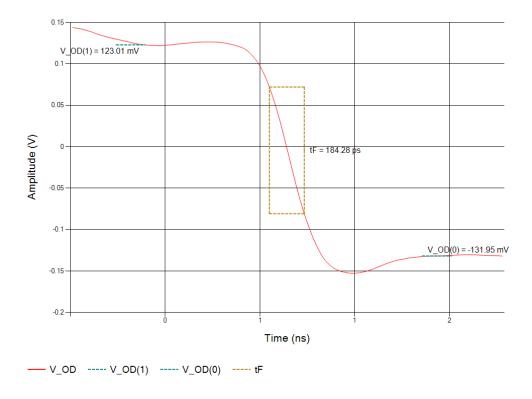

| 1.3.4 – Data Lane HS-TX Differential Voltages $V_{\text{OD}(0)}$ and $V_{\text{OD}(1)}$          |      |

| 1.3.5 – Data Lane HS-TX Differential Voltage Mismatch $\Delta V_{OD}$                            |      |

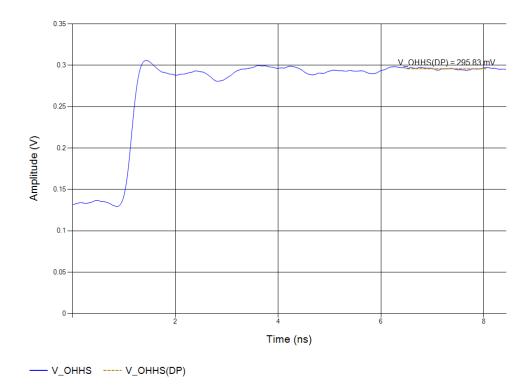

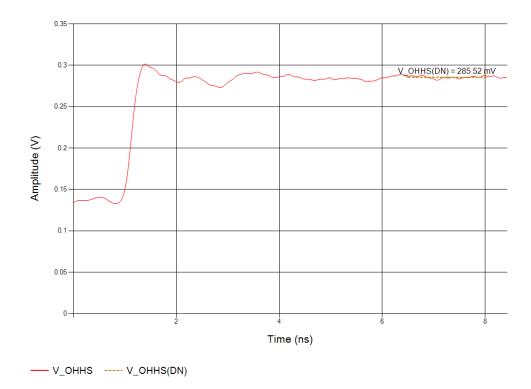

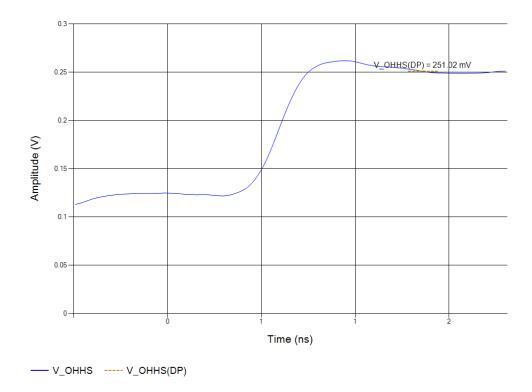

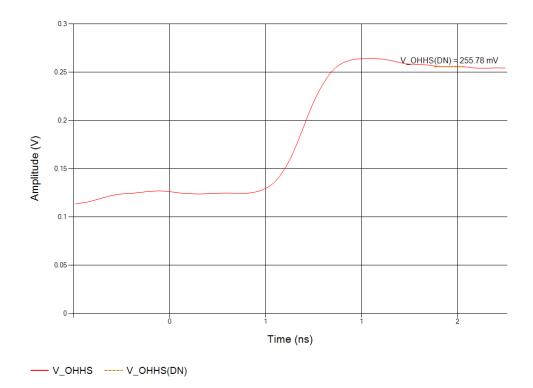

| 1.3.6 – Data Lane HS-TX Single-Ended Output Voltages $V_{OHHS(DP)}$ and $V_{OHHS(DN)}$           |      |

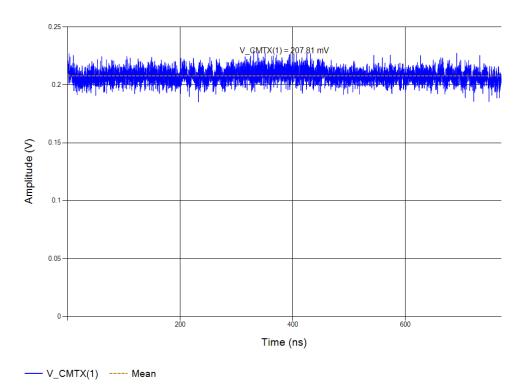

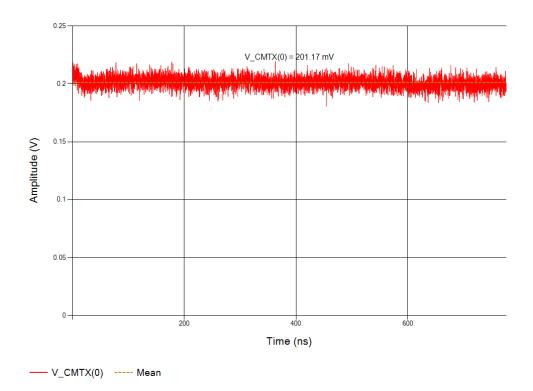

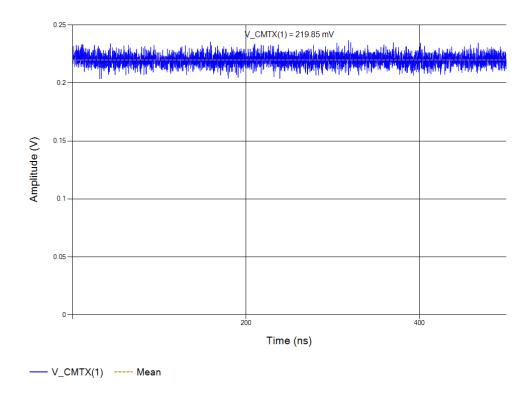

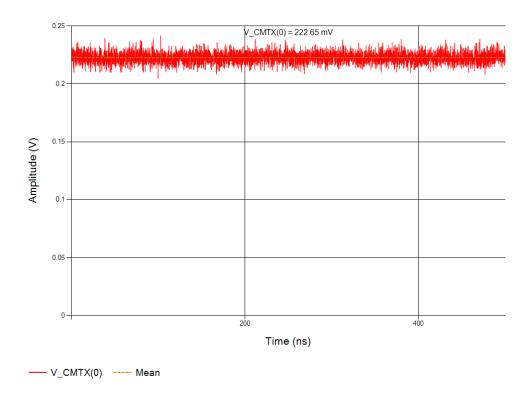

| 1.3.7 – Data Lane HS-TX Static Common-Mode Voltages $V_{CMTX(1)}$ and $V_{CMTX(0)}$              |      |

| 1.3.8 – Data Lane HS-TX Static Common-Mode Voltage Mismatch $\Delta V_{CMTX(1,0)}$               |      |

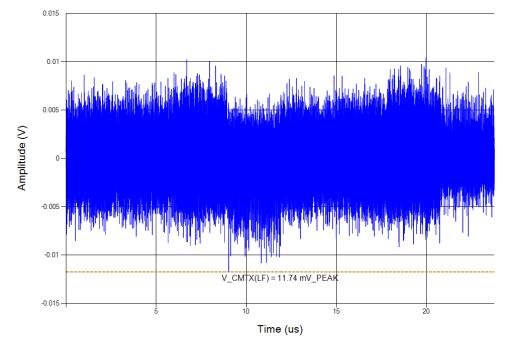

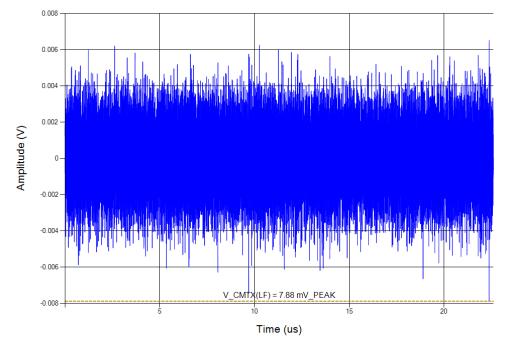

| 1.3.9 – Data Lane HS-TX Dynamic Common-Level Variations Between 50-450 MHz $\Delta V_{CMTX(LF)}$ |      |

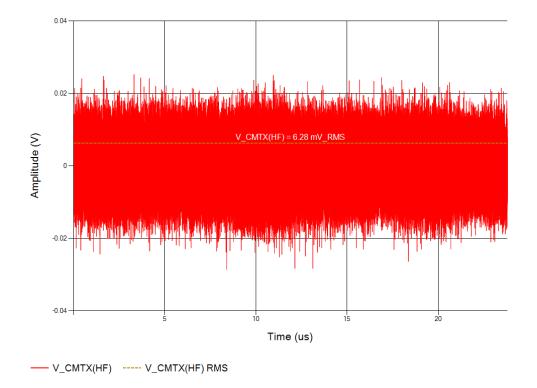

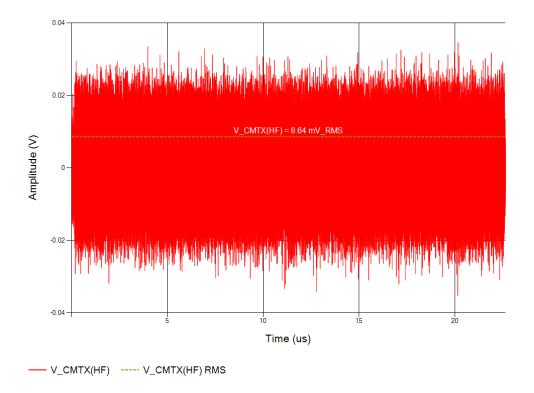

| 1.3.10 – Data Lane HS-TX Dynamic Common-Level Variations Above 450 MHz $\Delta V_{CMTX(HF)}$     |      |

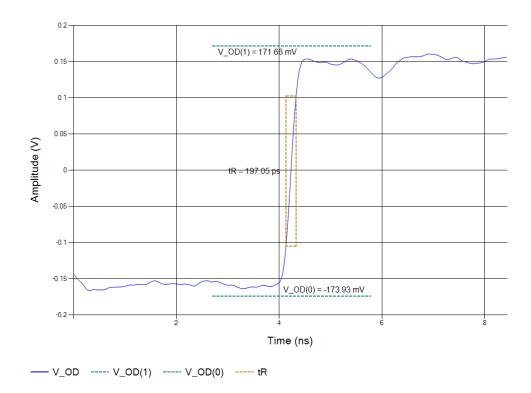

| 1.3.11 – Data Lane HS-TX 20%-80% Rise Time t <sub>R</sub>                                        |      |

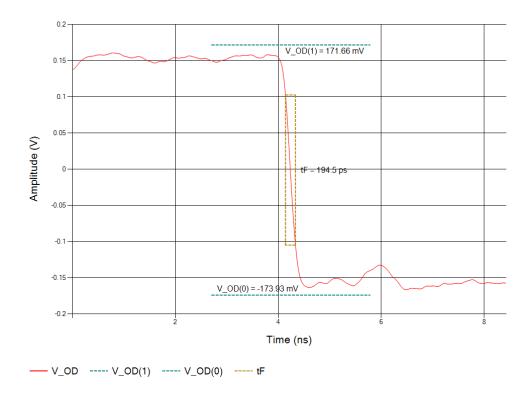

| 1.3.12 – Data Lane HS-TX 80%-20% Fall Time t <sub>F</sub>                                        |      |

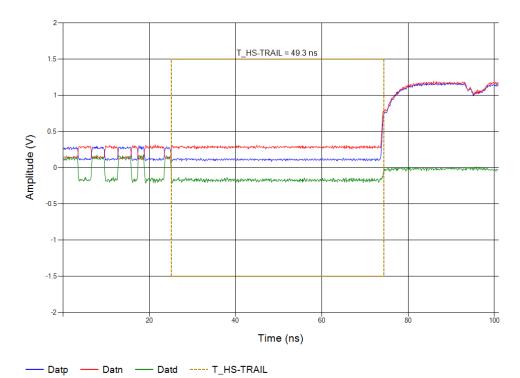

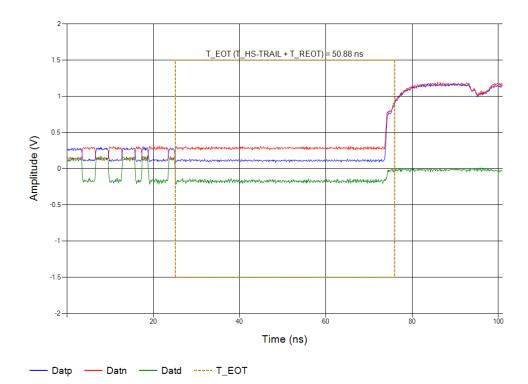

| 1.3.13 – Data Lane HS Exit: T <sub>HS-TRAIL</sub> Value                                          |      |

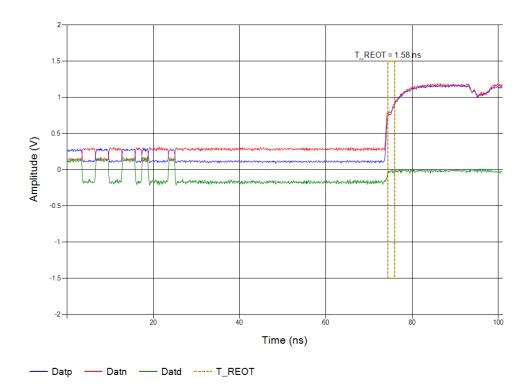

| 1.3.14 – Data Lane HS Exit: 30%-85% Post-EoT Rise Time T <sub>REOT</sub>                         |      |

| 1.3.15 – Data Lane HS Exit: T <sub>EOT</sub> Value                                               |      |

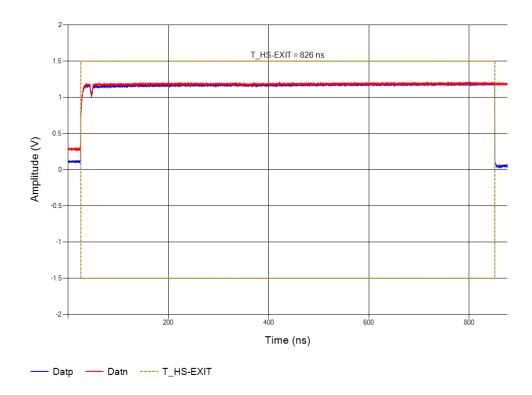

| 1.3.16 – Data Lane HS Exit: T <sub>HS-EXIT</sub> Value                                           |      |

| Test Groups and Tests                                                                                               | see  |

|---------------------------------------------------------------------------------------------------------------------|------|

| Group 4 (18 tests): Clock Lane HS-TX Signaling Requirements                                                         | page |

| 1.4.1 – Clock Lane HS Entry: T <sub>LPX</sub> Value                                                                 | 66   |

| 1.4.2 – Clock Lane HS Entry: T <sub>CLK-PREPARE</sub> Value                                                         |      |

| 1.4.3 – Clock Lane HS Entry: T <sub>CLK-PREPARE</sub> + T <sub>CLK-ZERO</sub> Value                                 |      |

| 1.4.4 – Clock Lane HS-TX Differential Voltages $V_{\text{OD}(0)}$ and $V_{\text{OD}(1)}$                            |      |

| 1.4.5 – Clock Lane HS-TX Differential Voltage Mismatch $\Delta V_{\text{OD}}$                                       |      |

| 1.4.6 – Clock Lane HS-TX Single-Ended Output Voltages $V_{\text{OHHS}(\text{DP})}$ and $V_{\text{OHHS}(\text{DN})}$ |      |

| 1.4.7 – Clock Lane HS-TX Static Common-Mode Voltages $V_{\text{CMTX}(1)}$ and $V_{\text{CMTX}(0)}$                  |      |

| 1.4.8 – Clock Lane HS-TX Static Common-Mode Voltage Mismatch $\Delta V_{CMTX(1,0)}$                                 |      |

| 1.4.9 – Clock Lane HS-TX Dynamic Common-Level Variations Between 50-450 MHz $\Delta V_{\text{CMTX(LF)}}$            |      |

| 1.4.10 – Clock Lane HS-TX Dynamic Common-Level Variations Above 450 MHz $\Delta V_{\text{CMTX(HF)}}$                |      |

| 1.4.11 – Clock Lane HS-TX 20%-80% Rise Time t <sub>R</sub>                                                          |      |

| 1.4.12 – Clock Lane HS-TX 80%-20% Fall Time t <sub>F</sub>                                                          |      |

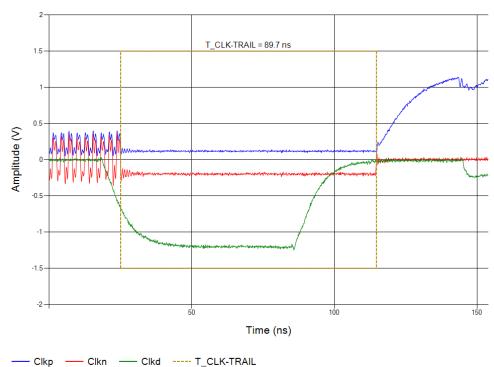

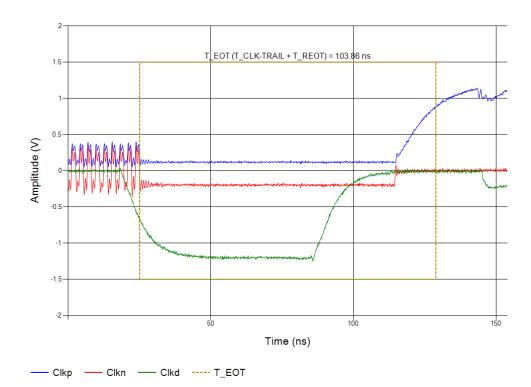

| 1.4.13 – Clock Lane HS Exit: T <sub>CLK-TRAIL</sub> Value                                                           |      |

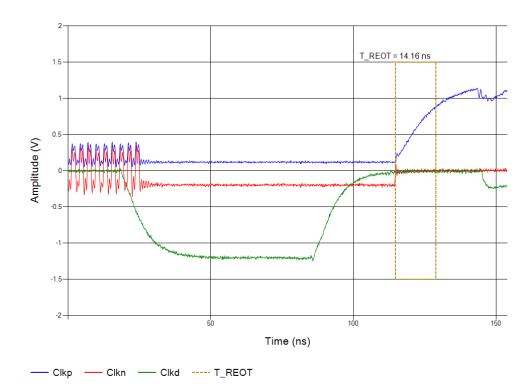

| 1.4.14 – Clock Lane HS Exit: 30%-85% Post-EoT Rise Time T <sub>REOT</sub>                                           |      |

| 1.4.15 – Clock Lane HS Exit: T <sub>EOT</sub> Value                                                                 |      |

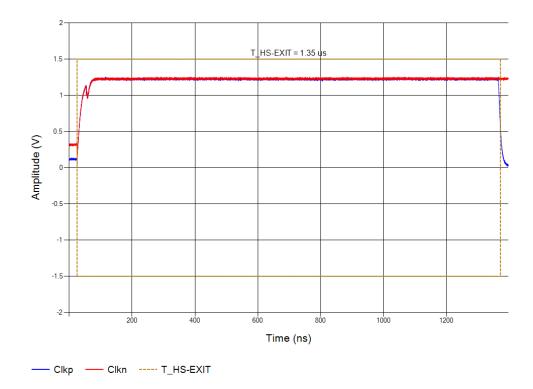

| 1.4.16 – Clock Lane HS Exit: T <sub>HS-EXIT</sub> Value                                                             |      |

| 1.4.17 – Clock Lane HS Clock Instantaneous: UI <sub>INST</sub> Value                                                |      |

| 1.4.18 – Clock Lane HS Clock Delta UI: (ΔUI) Value                                                                  |      |

| Group 5 (4 tests): HS-TX Clock-to-Data Lane Timing Requirements                                                     | page |

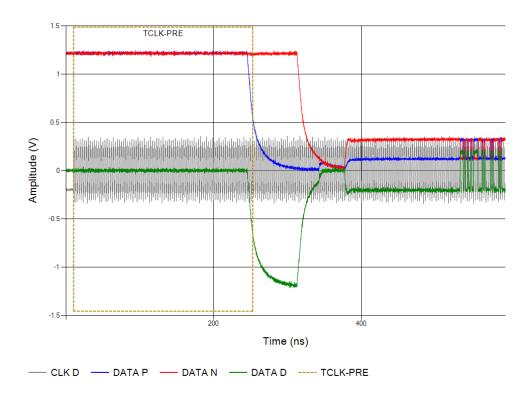

| 1.5.1 – HS Entry: T <sub>CLK-PRE</sub> Value                                                                        | 91   |

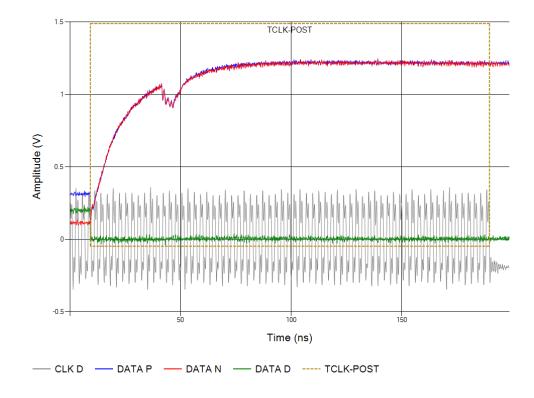

| 1.5.2 – HS Exit: T <sub>CLK-POST</sub> Value                                                                        |      |

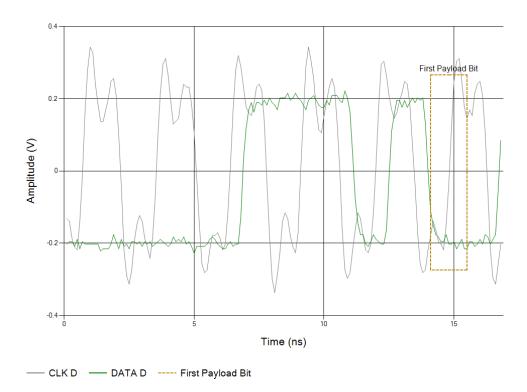

| 1.5.3 – HS Clock Rising Edge Alignment to First Payload Bit                                                         |      |

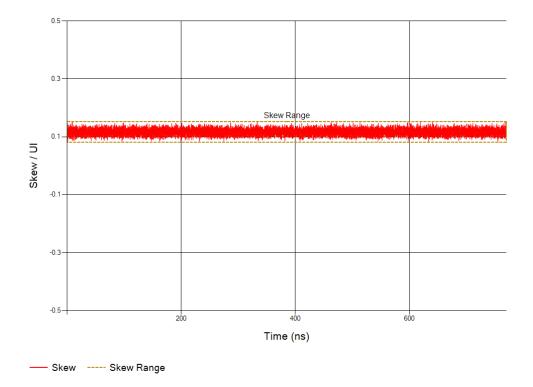

| 1.5.4 – Data-to-Clock Skew (T <sub>SKEW[TX]</sub> )                                                                 |      |

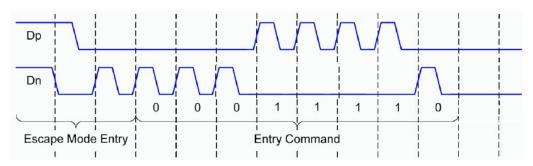

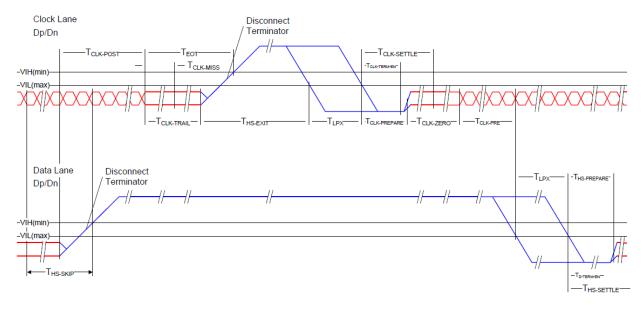

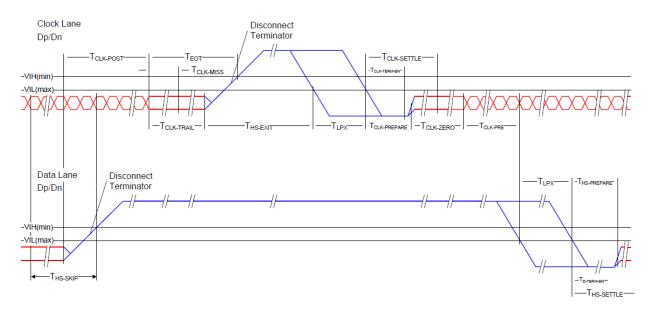

Any D-PHY configuration consists of at least one clock lane module, and one or several data lane modules. Each module provides a synchronized connection between master and slave. During normal operation, a lane switches between the modes "low power" (LP) and "high speed" (HS). High speed functions are used for HS data transmission in bursts with an arbitrary number of payload data bytes. Low power functions are mainly used for control, but have other optional use cases, like LP escape mode. The presence of HS and LP functions is correlated.

| Starting D-PHY Compliance Tests                        |    |

|--------------------------------------------------------|----|

| Test Configuration for D-PHY                           |    |

|                                                        |    |

| Clock Lane LP-TX Signaling Requirements (Group 2)      |    |

| Data Lane HS-TX Signaling Requirements (Group 3)       |    |

| Clock Lane HS-TX Signaling Requirements (Group 4)      | 66 |

| HS-TX Clock-to-Data Lane Timing Requirements (Group 5) |    |

|                                                        |    |

## 4.1 Starting D-PHY Compliance Tests

Before you run the test, complete the following actions:

- Initial setup of the equipment, see Chapter 2.2, "Installing Software and License", on page 7

- LAN connection of the oscilloscope and the computer running the R&S Scope-Suite, see Chapter 2.5, "Connecting the R&S RTO", on page 9

- 1. Select "D-PHY" in the R&S ScopeSuite start window.

- 2. In the "Session Selection" dialog, add a new test session and open it, see Chapter 3.1, "Starting a Test Session", on page 12.

- 3. Check the test configuration settings and adjust, if necessary. See:

- Chapter 3.2.1.1, "Limit Manager", on page 14

- Chapter 4.2, "Test Configuration for D-PHY", on page 19 Specific information on the required settings is given in the "Test Requirements" chapters for each test group.

- 4. Select/check the test cases you want to run and click "Test Single"/"Test checked".